曼切斯特加法器

曼切斯特加法器

传统的行波进位加法器慢,是因为进位信号必须经过每一级的复杂逻辑门(与非门、或非门等)才能传到下一级。

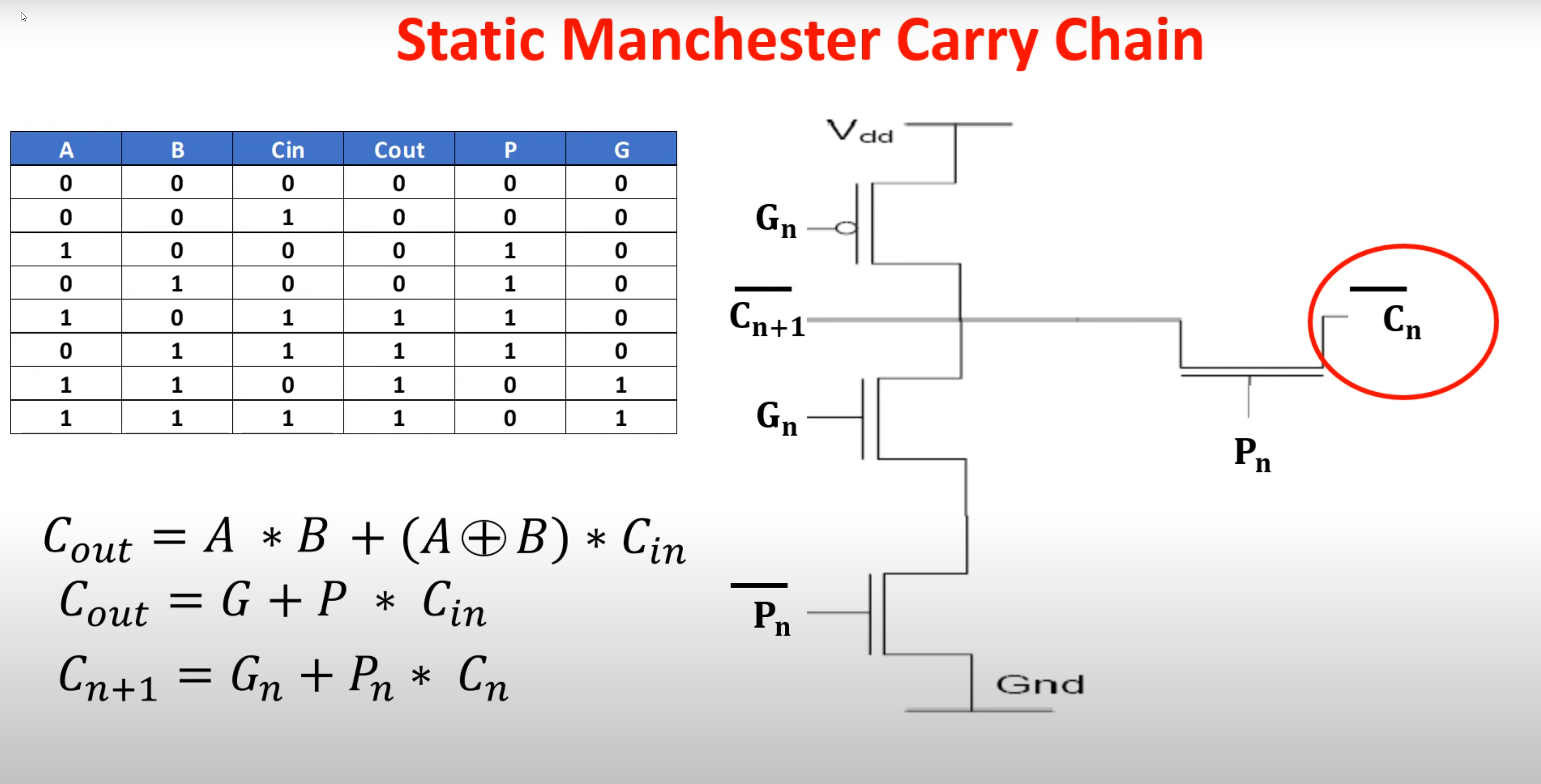

曼彻斯特进位链通过定义三个状态,利用开关电路直接导通进位:

基本状态

- 生成 (Generate, ) : 。无论低位进位如何,当前位必然产生进位。

- 传播 (Propagate, ) : (即其中一个是 1)。如果低位有进位,直接通过当前位传给高位。

- 消除 (Kill/Delete, ) : 。无论低位进位如何,进位在此截断。

逻辑公式:

结构组成

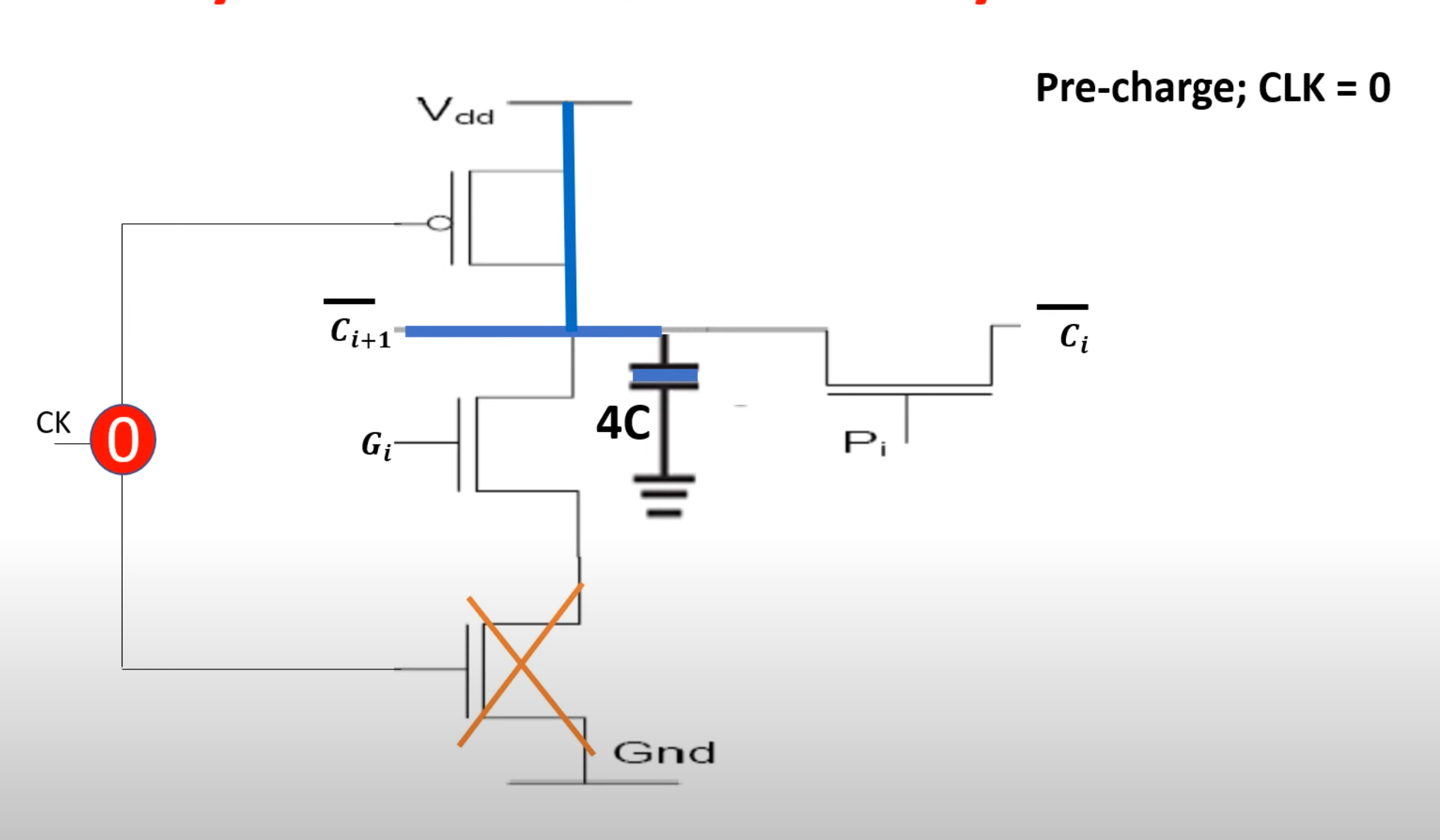

预充电路(Precharge) : 在时钟 为低电平时,将进位节点预充电到高电平(VDD)。

进位链(The Chain) :

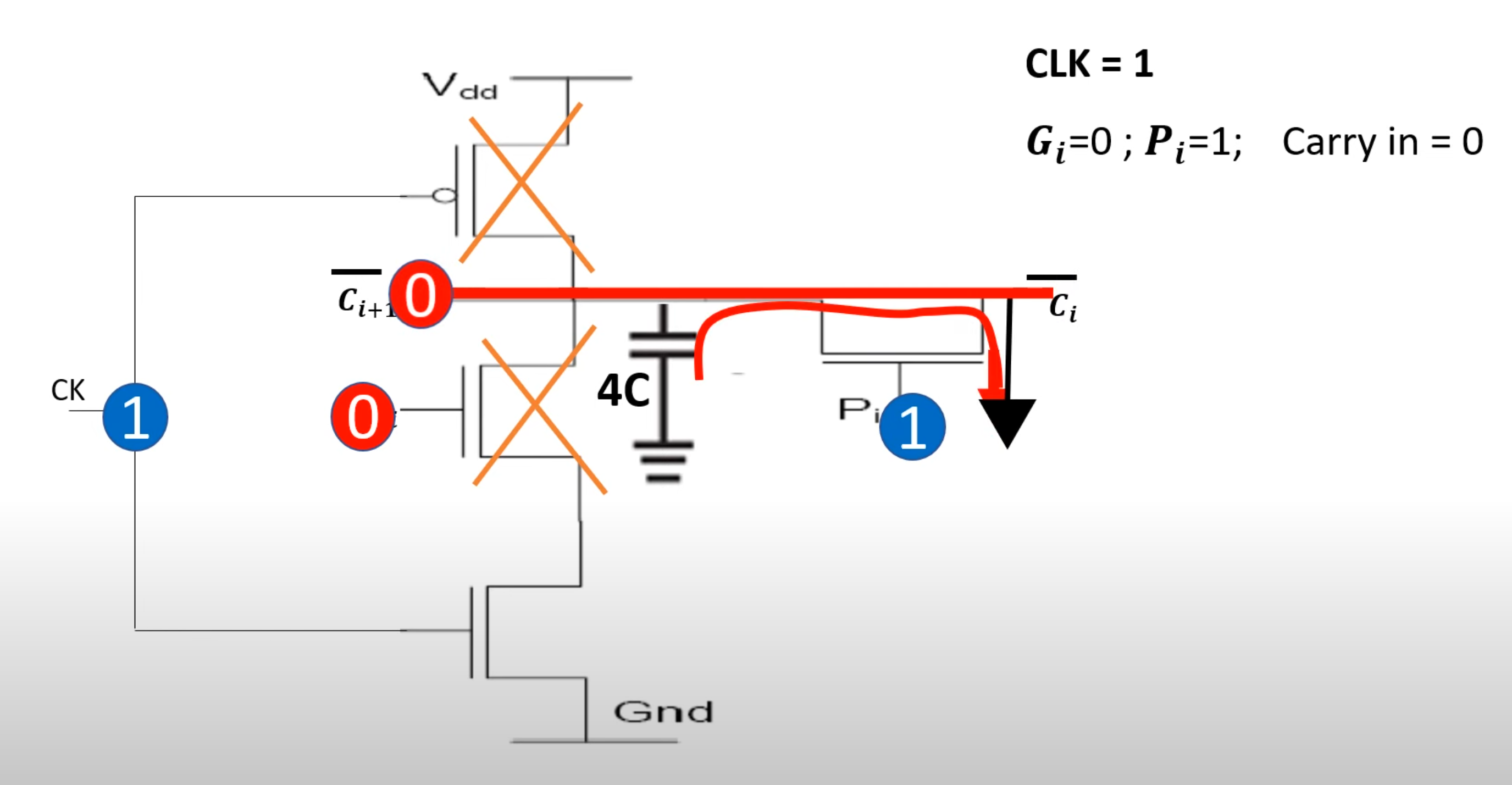

- 传输开关: 由 控制的 NMOS 传输管串联在一起。如果 为高,进位信号 直接“流”向 。

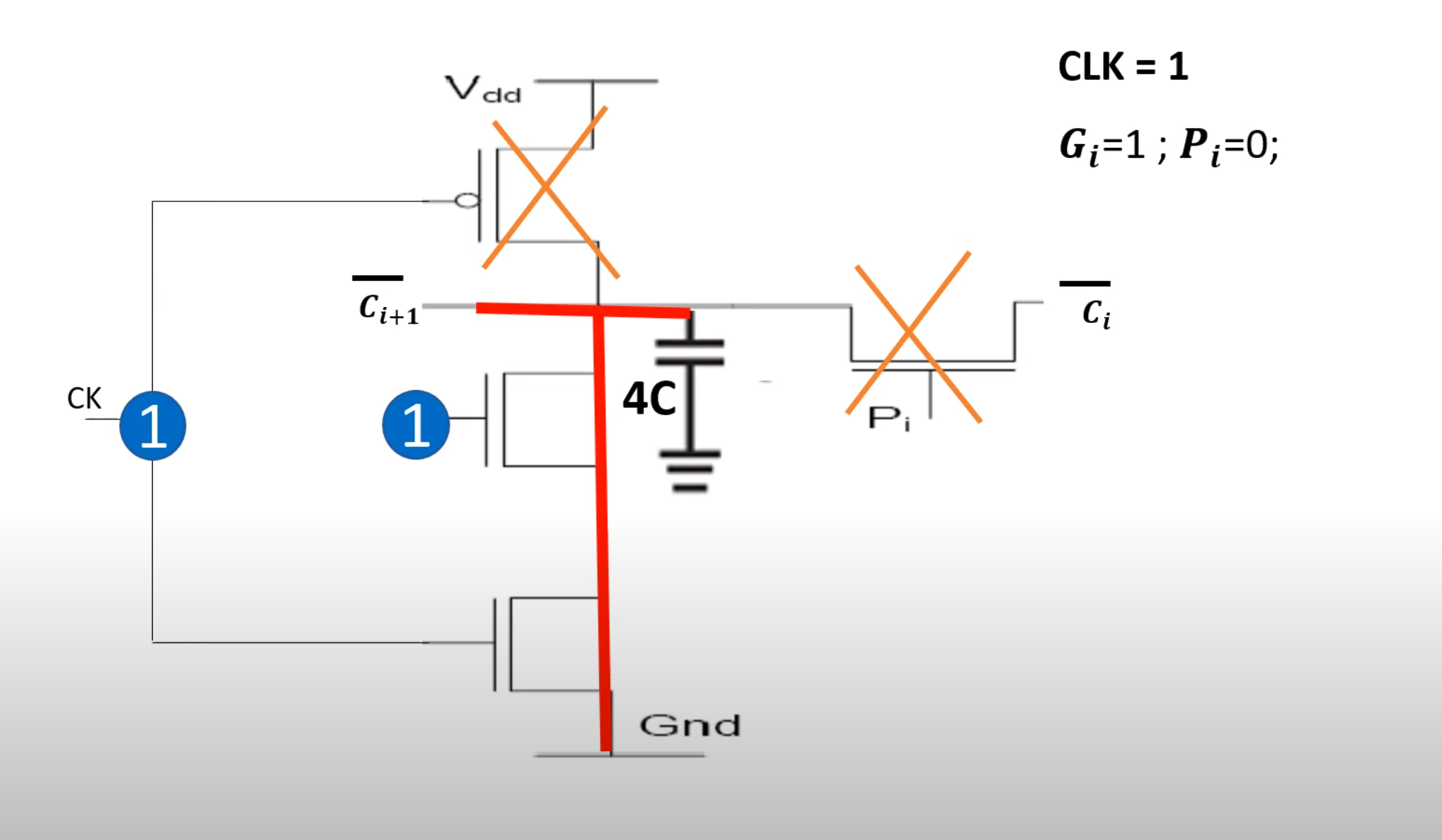

- 下拉路径: 由 控制的 NMOS 管接地。如果 为高,直接将 节点拉低(表示产生反向逻辑的进位,或者根据具体逻辑极性设计)。

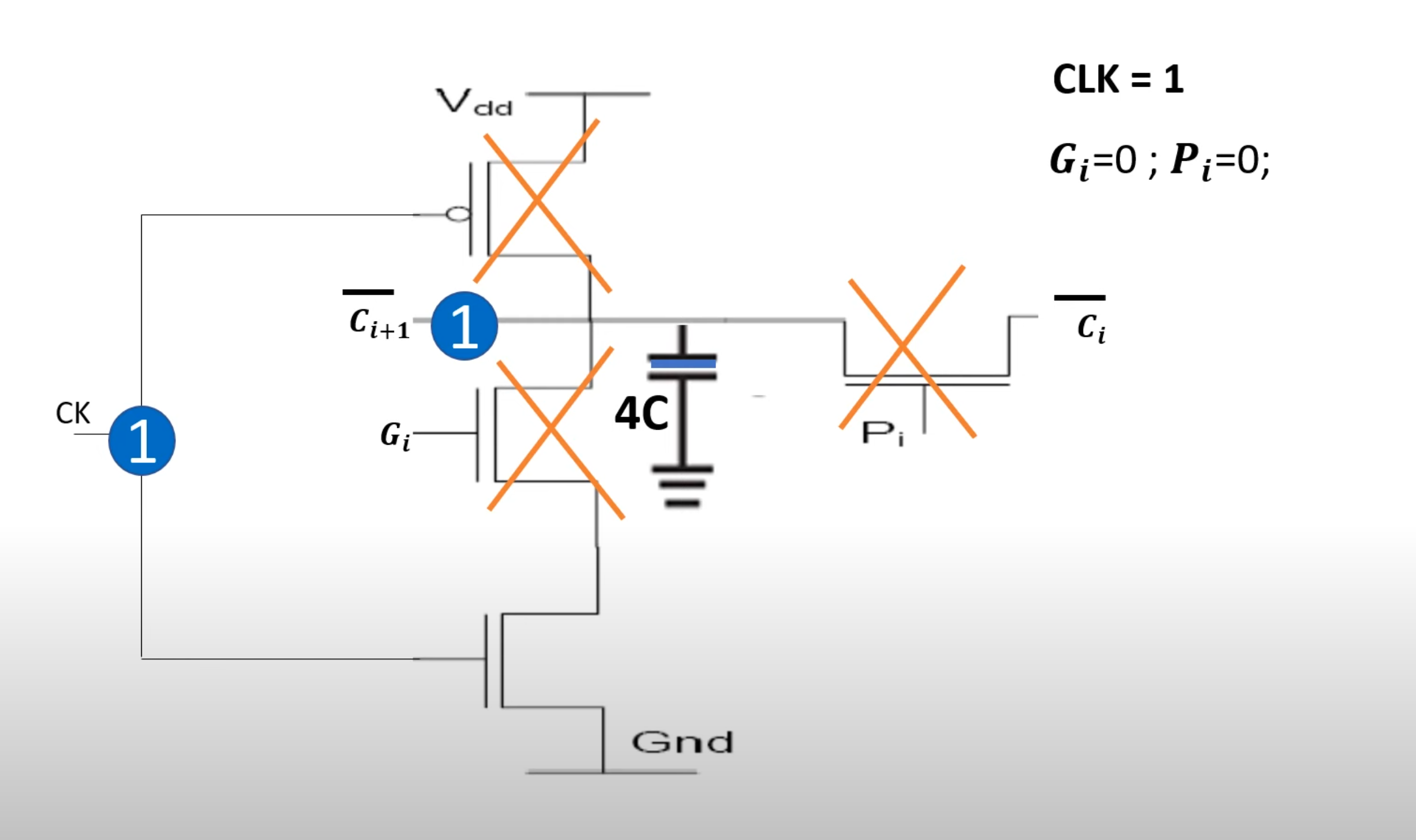

求值(Evaluate) : 时钟 变为高电平时,电路根据输入 和 的状态决定节点电平。

预充电

求值 CLK = 1

GI=0 ; PI=0

GI=1;PI=0

GI=0;PI=1;CARRY IN =0

总的电路

真值表:动态门 推出逻辑表达式

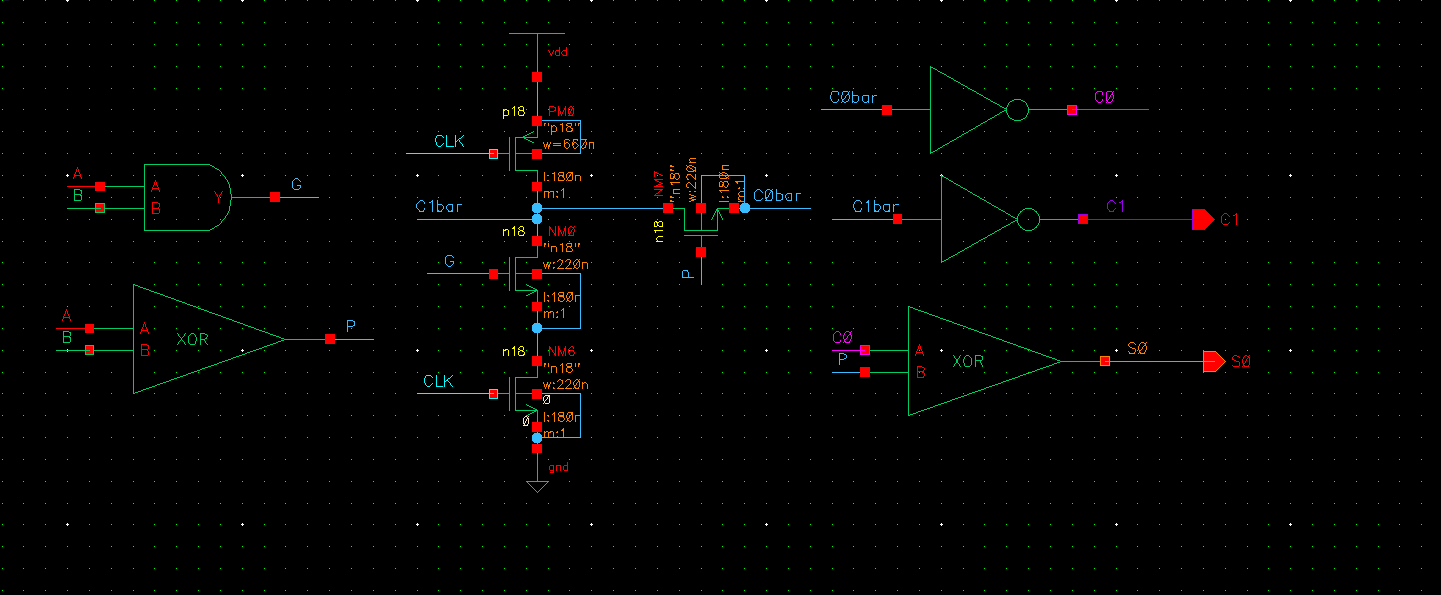

schematic

1bit 曼切斯特加法器原理图

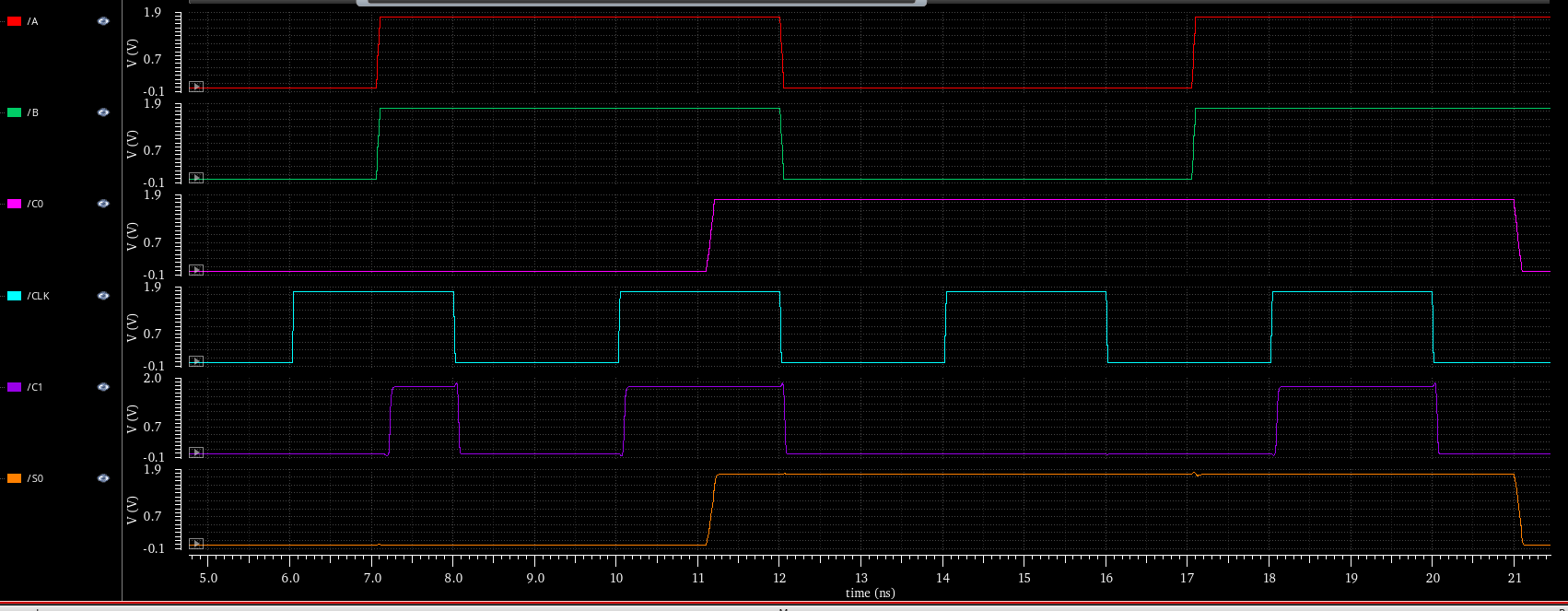

仿真波形图

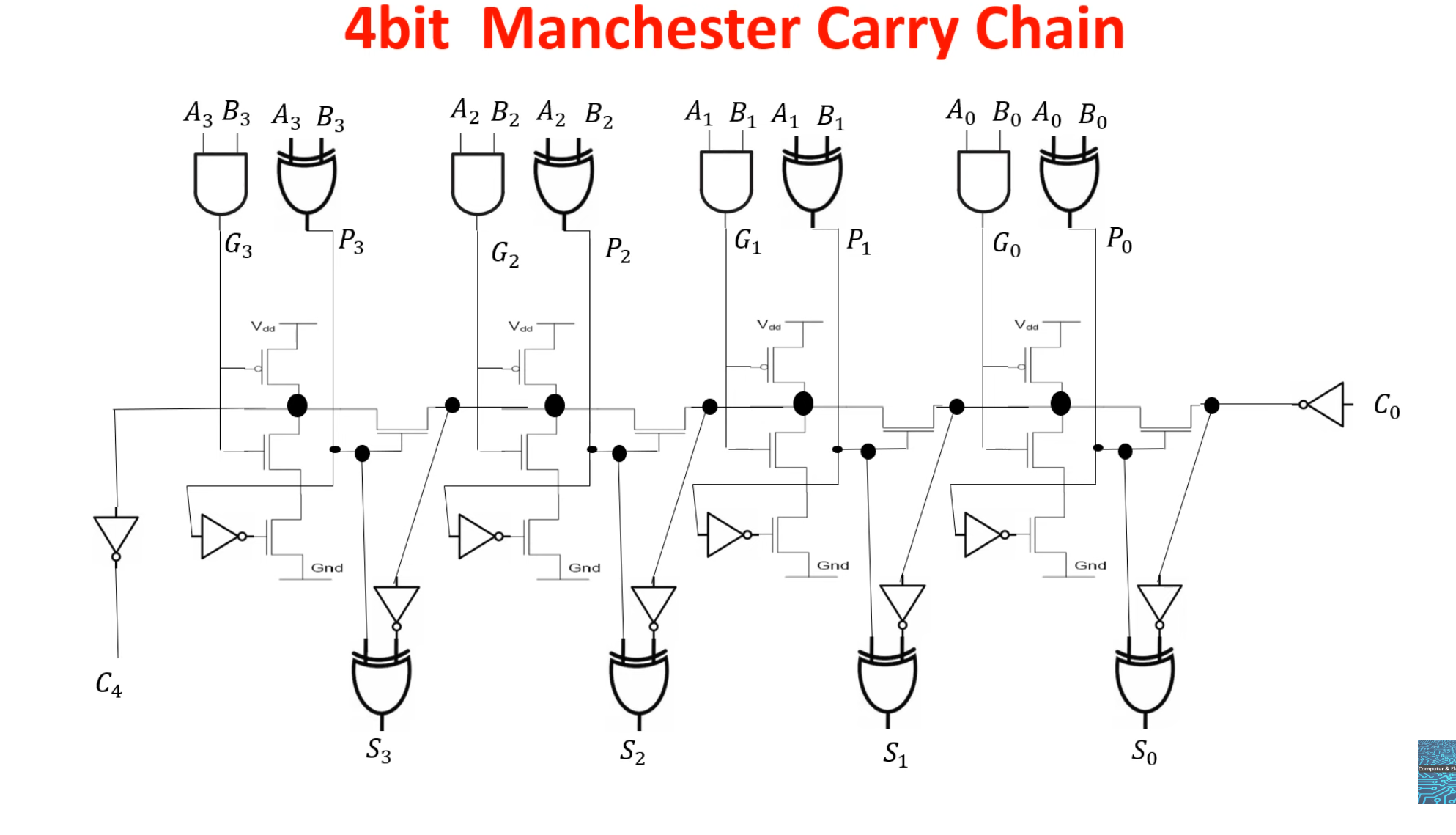

4bit 曼切斯特加法器原理图

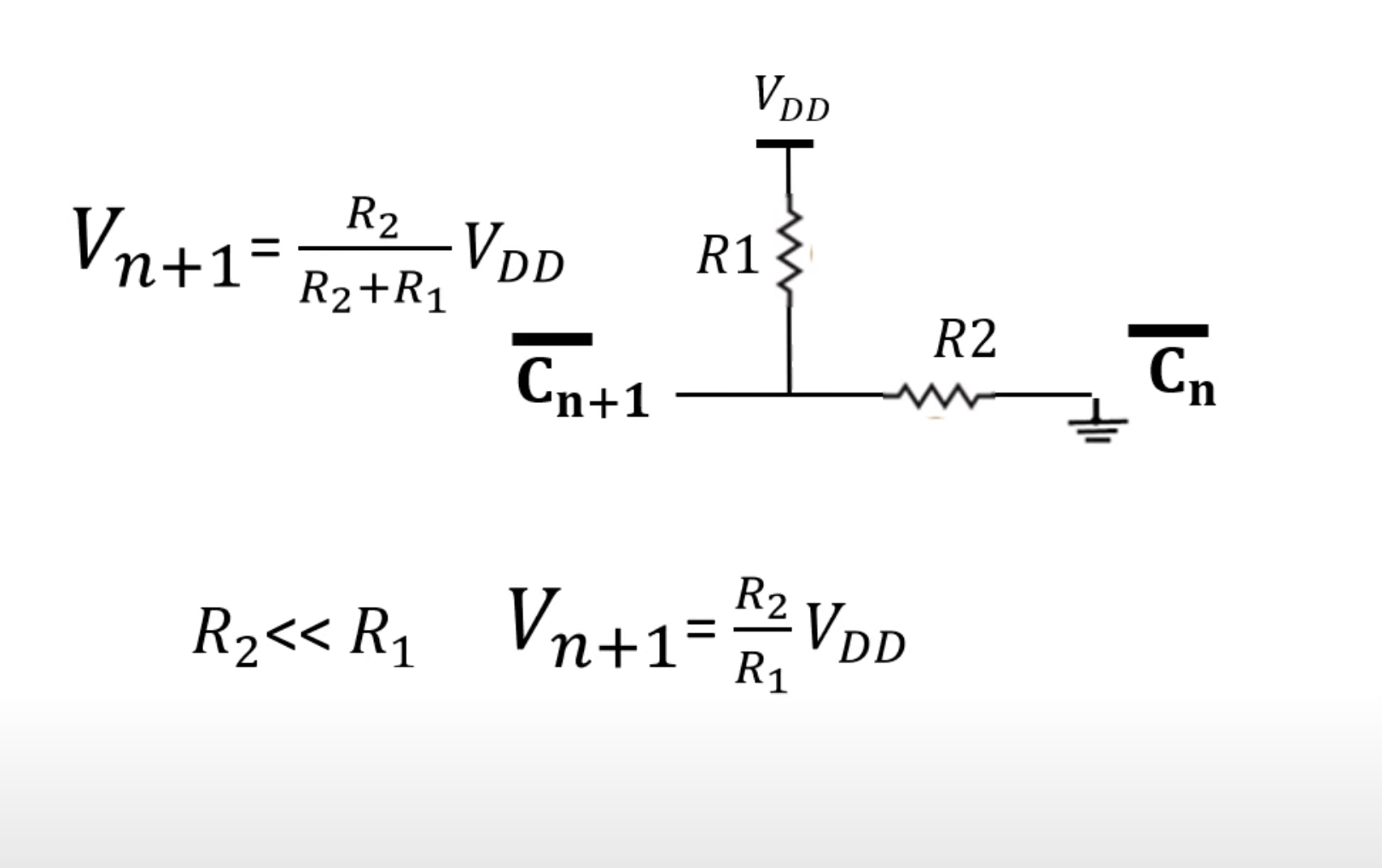

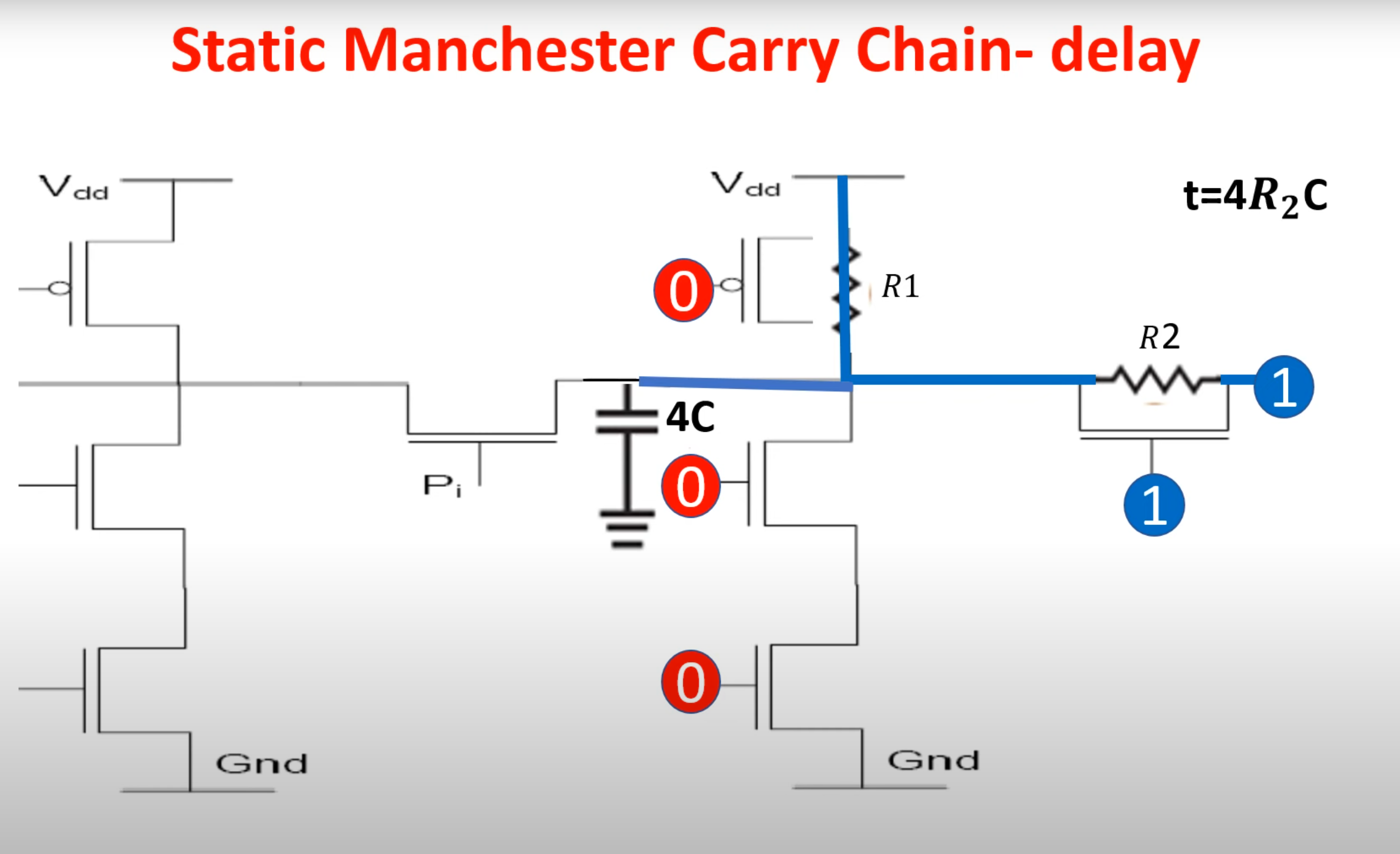

静态电阻

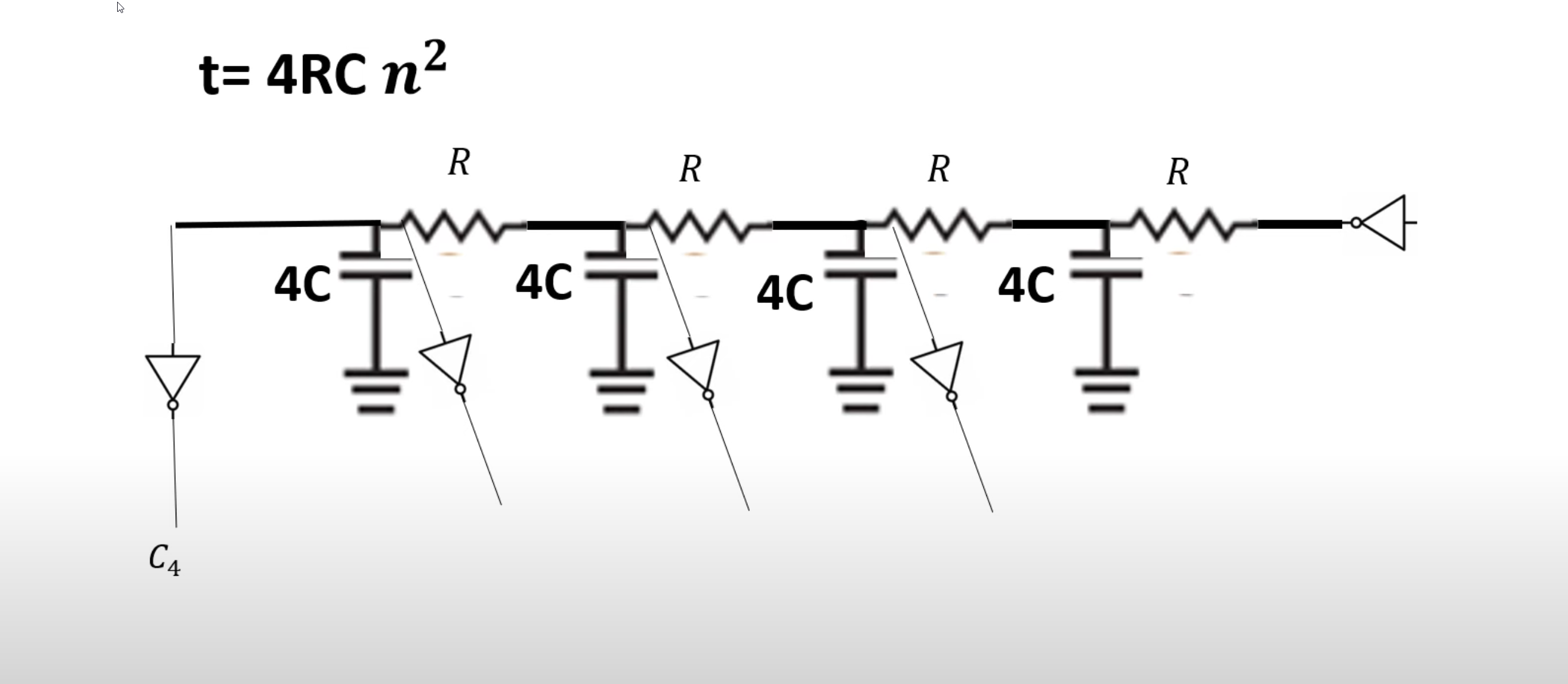

延时

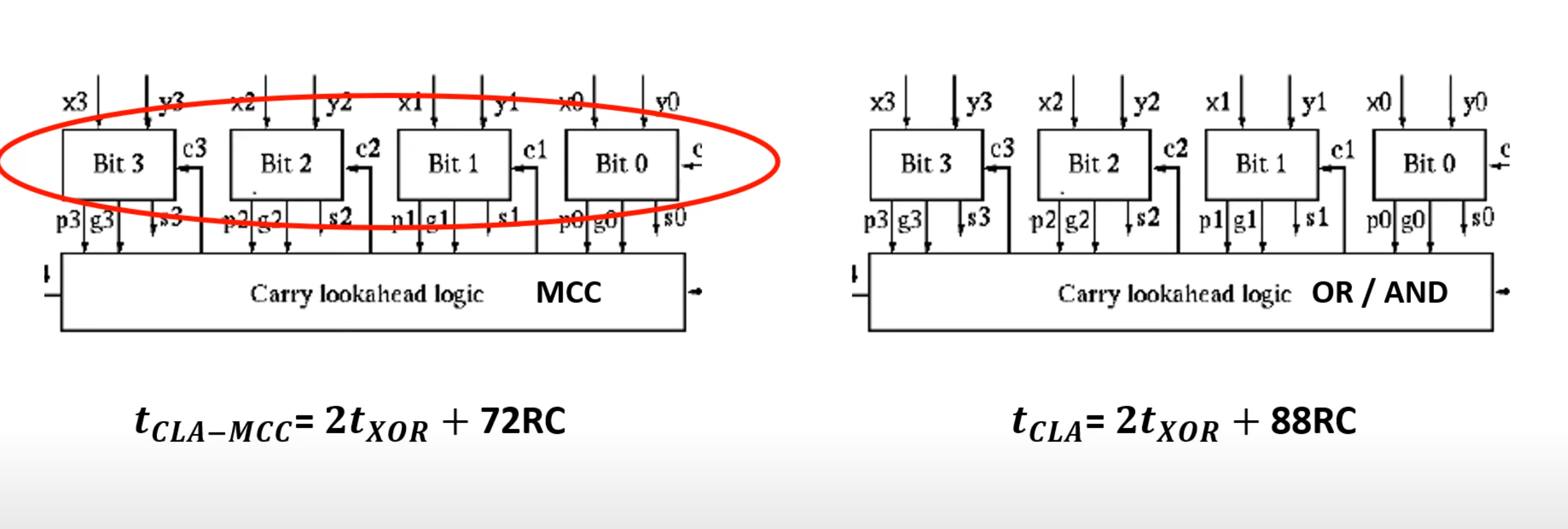

延时对比

右图:常规静态 CLA,传统的静态 CMOS 逻辑门, 它通过纯粹的布尔代数公式计算进位。

节点电容大,且信号要经过好几级门的翻转

左图:曼彻斯特,传输管或动态逻辑开关, 利用开关网络让电流直接流过 。